本文全面解析了组合逻辑电路的设计与测试,从理论到实践进行了详细阐述。首先介绍了组合逻辑电路的基本概念和原理,包括逻辑门、逻辑函数、卡诺图等。文章详细讲解了组合逻辑电路的设计方法,包括逻辑表达式化简、卡诺图化简、布尔代数化简等,并介绍了使用硬件描述语言(如VHDL、Verilog)进行设计的方法。在测试方面,文章介绍了组合逻辑电路的测试策略和测试方法,包括功能测试、时序测试、故障注入测试等,并介绍了使用测试向量生成和故障模拟软件进行测试的方法。文章还探讨了组合逻辑电路的优化和改进方法,包括逻辑门级优化、布局优化、时序优化等。通过本文的全面解析,读者可以深入了解组合逻辑电路的设计与测试的各个方面,为实际工程应用提供有力支持。

在数字电子系统设计中,组合逻辑电路扮演着至关重要的角色,它们根据输入信号的当前状态,在有限的时间内产生输出结果,无需记忆或存储任何数据,本文将深入探讨组合逻辑电路的设计原理、方法、以及测试策略,旨在为电子工程师和设计者提供一套全面而实用的指导。

一、组合逻辑电路基础

组合逻辑电路由逻辑门(如AND、OR、NOT、XOR等)和更复杂的逻辑单元(如解码器、编码器、多路选择器等)组成,其核心在于根据输入信号的组合,通过布尔代数运算规则,直接产生输出结果,设计时需遵循的基本原则包括:

正确性:确保电路的逻辑功能符合设计要求。

可靠性:在各种工作条件下保持稳定性能。

可测试性:便于进行故障检测和诊断。

优化:在满足功能要求的前提下,尽量减少资源消耗(如门数、延迟等)。

二、组合逻辑电路的设计步骤

1、需求分析:明确电路的输入、输出以及它们之间的关系,即逻辑功能描述,这通常通过真值表、逻辑表达式或状态机等形式表达。

2、逻辑设计:根据需求分析结果,使用布尔代数、卡诺图化简或Quine-McCluskey算法等方法,设计出实现所需功能的逻辑表达式或电路结构。

3、硬件实现:将逻辑设计转化为实际的硬件电路,这包括选择合适的逻辑门和元件,进行布局布线,并考虑信号的传播延迟和资源利用率。

4、仿真验证:利用数字电路仿真软件(如SPICE、VHDL、Verilog等)对设计进行模拟测试,验证其逻辑功能和性能指标是否符合预期。

5、优化与调整:根据仿真结果进行必要的优化和调整,以提高效率、降低功耗或改善时序性能。

三、组合逻辑电路的测试策略

1、功能测试:通过向电路输入所有可能的输入组合,检查输出是否与预期的真值表一致,这是验证电路功能正确性的基本方法。

2、时序测试:对于有严格时序要求的组合逻辑电路,需测试其输出响应时间是否满足设计要求,这包括信号传播延迟、建立时间和保持时间等参数的测量。

3、稳定性测试:在各种工作条件下(如温度变化、电源波动等),持续观察电路的输出稳定性,确保其能在恶劣环境下正常工作。

4、故障注入测试:通过模拟硬件故障(如门失效、线路干扰等),评估电路的容错能力和可靠性,这通常需要使用专业的测试设备和软件进行。

5、性能评估:除了功能正确性外,还需评估电路的功耗、面积(占用空间)、速度等性能指标,确保其满足实际应用需求。

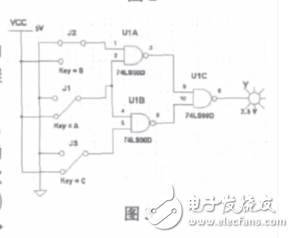

四、设计实例:四路选择器设计及测试

以四路选择器(Multiplexer, MUX)为例,其功能是根据选择信号的不同,从四个输入信号中选择一个输出,设计时首先根据需求分析确定其真值表:

| 输入A | 输入B | 输入C | 选择S | 输出Y |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 0 |

| ... | ... | ... | ... | ... |

| 1 | 1 | 1 | 1 | 1 |

接下来使用卡诺图化简或布尔代数方法得到其逻辑表达式:$Y = \overline{S}A + S(\overline{B}C + BC\overline{D} + B\overline{C}D)$,并据此设计硬件电路,完成设计后,使用仿真软件进行功能、时序和稳定性测试,确保其符合预期,进行实际布板和测试,验证其在实际应用中的表现。

五、挑战与未来趋势

尽管组合逻辑电路在数字系统中应用广泛且成熟,但随着技术的发展,仍面临一些挑战:如低功耗设计、高速信号处理、容错计算等,未来趋势包括:

低功耗设计:采用新型材料(如FinFETs)、动态电压调节和门控技术等手段降低功耗。

高速信号处理:利用更先进的工艺(如EUV光刻)和优化算法提高信号传输速度和效率。

容错计算:在关键应用中引入冗余和错误校正技术,提高系统的可靠性和稳定性。

京公网安备11000000000001号

京公网安备11000000000001号 京ICP备11000001号

京ICP备11000001号